基于FPGA的RapidIO接口仿真验证实现方法

作者简介

姚春月,男,计算机科学与技术学士,工程师。曾负责多个航天器、军工重点型号FPGA的第三方评测,主要从事通用控制类FPGA相关测试技术的研究。

摘要:

随着集成电路和光纤传输技术的飞速发展,RapidIO以其具有高性能、高可靠性、低引脚数和结构灵活等特点,被大量用在嵌入式系统中。在以RapidIO为接口的FPGA设计中,对RapidIO IP核的验证是其基础。设计前期通过功能仿真,可以在没有硬件支持的情况下,尽早发现其中的问题,可以大大提高工作效率和加快研制进度。文中介绍了验证平台的搭建过程,包括RapidIO IP核的生成及其内部结构,仿真环境的建立等。对于类似项目,可以参考文中仿真验证平台搭建过程,轻松复现测试过程,具有一定的通用性。

关键词:RapidIO;仿真;验证;FPGA

引言

RapidIO总线多芯片间互连通信技术一般用于实现现场可编程门阵列(FPGA)与数字信号处理器(DSP)、FPGA与FPGA、FPGA与通用处理器(PPC)之间互连通信。通过使用FPGA官方自带的ip核,可以快速完成相关功能的建立,而对数据帧的解析则需要自行编写。对ip核进行功能仿真,可以更早更准确的定位解析中的设计问题,并能达到更加理想代码覆盖率和功能覆盖率,有效提高了验证效率。

1、RapidIO协议

RapidIO是为了实现高带宽高稳定性目标而发展的。采用了三层分级体系结构:逻辑层、传输层和物理层。如图1.1所示。

图1.1 RapidIO协议架构

1.1 逻辑层

逻辑层处于最上层,主要负责I/O操作、消息传递、共享存储、流量控制等功能,作为使用IP核进行FPGA开发,逻辑层编写正确与否直接决定着功能是否能够正确实现。

1.1.1 I/O操作

RapidIO定义了6种基本的I/O操作,分别为读操作(NREAD、RESPONSE),写操作(NWRITE),有响应的写操作(NWRITE_R、RESPONSE),流写操作(SWRITE),Atomic(读-修改-写)操作(ATOMIC、RESPONSE)和维护操作(MAINTENANCE)。

读操作流程为发起方通过NREAD事务向接收方发送读请求,接收方通过RESPONSE事务反馈发起方想要读取地址的数据。

写操作或有响应的写操作流程为发起方通过NWRITE事务或NWRITE_R事务向接收方发送写请求,接收方将发起方发送的数据写入对应地址,NWRITE_R事务接收方向发起方RESPONSE事务返回响应。

流写操作流程为是发起方通过SWRITE事务向接收方发送写请求,与NWRITE不同,SWRITE是用来向接收方写入大量数据的。

Atomic(读-修改-写)操作是读和写操作的组合,流程是发起方通过ATOMIC读取指定地址数据,接收方通过RESPONSE事务反馈发起方想要读取的数据,接收方根据ATOMIC中的指定操作,对读取的数据进行修改后,写回到接收方的指定地址。

维护操作不需要指定地址,用来访问RapidIO能力寄存器、状态寄存器和数据结构,维护写和维护读事务都必须产生正确的维护响应。

1.1.2 消息传递

消息传递分为门铃事务(Doobell)和消息事务(Message),门铃事务用于发送非常短的16位数据载荷,字段内容为可以根据功能需求进行自定义,消息事务(Message)与门铃事务的区别为最多可发送4096Byte的数据载荷,接收方接收到门铃事务(Doobell)和消息事务(Message)都需要反馈响应包,分为完成响应,重传响应和错误响应。

1.1.3 全局共享存储

全局共享存储器是RapidIO扩展功能,即可以把存储器放到系统中的不同位置,可以正确地在不同处理器件间缓存。

1.1.4 流量控制

流量控制是指采用某些规则和机制,控制事务处理的方式,避免系统死锁。

1.2 传输层

RapidIO传输层协议定义了一个标准传输机制,以此来说明添加到RapidIO逻辑数据包中的头信息,以及头信息被交换结构解释的方式,这些要求不依赖于物理层实现的机制,也独立于任何RapidIO逻辑层规范。对于使用IP核的开发者来说,不需要理解其特征,可以直接使用。

1.3 物理层

RapidIO物理层协议定义了一个器件间全双工的串行物理层连接。这种连接是由一个或多个通道组成,每个通道的每个方向上都是一对单向串行信号。同样对于使用IP核的开发者来说,不需要理解其特征,可以直接调用。

2、RapidIO验证方法

由于FPGA使用Xilinx自带IP核实现RapaidIO通信,传输层和物理层均由官方IP保证其正确性,因此可以将传输层和物理层作为黑盒,不用关心其内部实现方法。验证的主要内容是对FPGA逻辑层功能正确性进行确认。

2.1 验证平台的搭建

2.1.1 IP核生成

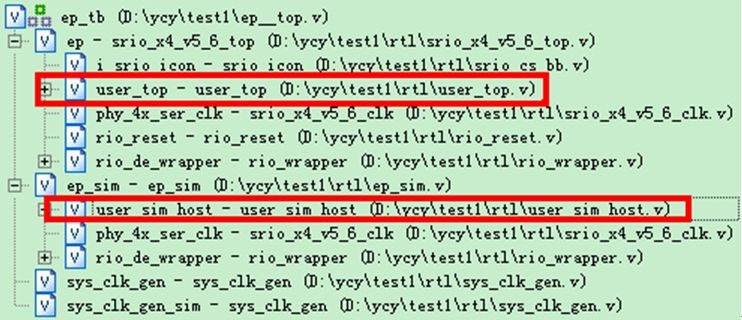

本文使用的ISE版本为14.7,利用其的CORE GENERATION,根据实际FPGA中RapidIO情况,选择对应的IP核,并生成相应的RTL代码,生成的代码结构如图2.1所示。

图2.1 RapidIO代码结构

其中ep_tb.v为顶层文件,sys_clk_gen.v为时钟产生文件,ep_sim.v模拟的是发送方,srio_x4_v5_6_top.v为模拟的为接收方。此工程可以直接进行仿真,内部有测试用数据的发送端和接收。user_sim_host.v中内部自带部分测试代码逻辑,主要是发送发送端发送的事务,包括I/O操作中NREAD、NWRITE、NWRITE_R、SWRITE和ATOMIC,以及消息传递中的Doobell和Message,user_top.v中内部自带代码主要是接收解析user_sim_host.v发送事务,以及通过RESPONSE对接收的事务进行反馈。

2.1.2 仿真工程搭建

被测试FPGA实现的功能是数字波束合成(DBF),数字波束合成技术是天线波束形成原理和数字信号处理技术相结合的产物,数字波束合成算法具有I/O数据传输率高、计算量大、实时性要求高等特点。具体相关功能为将外部ppc通过RapidIO发送的指令进行解析,并根据指令执行相应命令。因此进行仿真环境搭建时只需将srio_x4_v5_6_top.v的内容替换为被测DUT即可,其他不用进行改动,即可建立测试环境。

修改user_sim_host.v中内容,使其符合被测DUT要求。user_sim_host.v中包含2接口,分别为initiator和target,被测试FPGA中同样有initiator和target接口。各个接口中的信号名如图2.2所示。

图2.2 RapidIO ip核信号关系

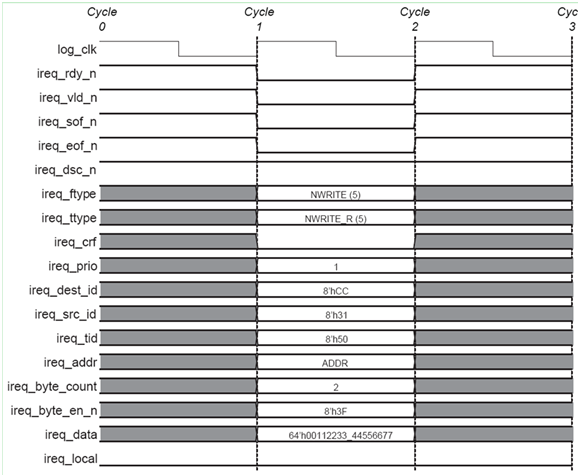

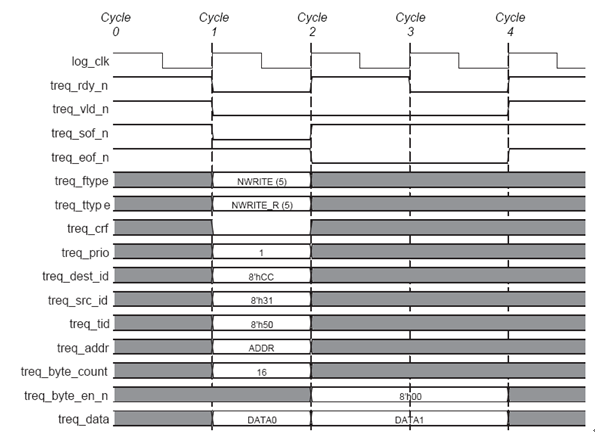

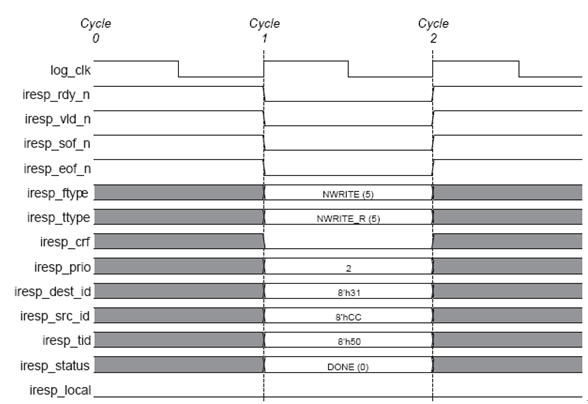

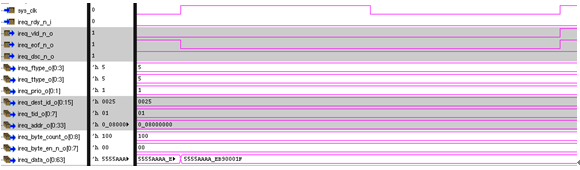

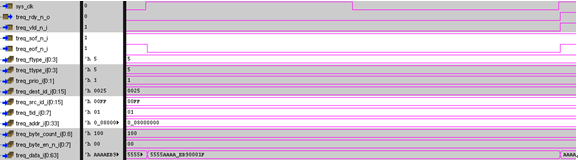

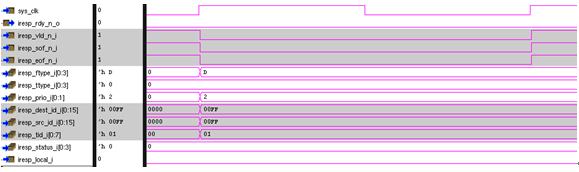

当测试激励中initiator接口的ireq接口向被测试FPGA按照NREAD、NWRITE、NWRITE_R、SWRITE或ATOMIC等操作对应的时序波形发送指令时,被测件中target接口的treq接口中就会出现与之对应的时序波形,以NWRITE_R为例,当测试激励中initiator接口的ireq接口发送波形时序满足图2.3时,被测件中target接口的treq接口接收到的波形如图2.4所示。被测件解析完指令后,通过target接口的tresp接口发送RESPONSE,测试激励中initiator接口的iresp接口接收到RESPONSE的波形如图2.5所示,整个NWRITE_R流程结束。

图2.3 IREQ端NWRITE_R时序图

图2.4 TREQ端NWRITE_R时序图

图2.5 IRESP端NWRITE_R时序图

测试激励和被测FPGA是2个独立的IP核。进行测试就会出现4个相互对应的通道。

1. 测试激励的initiator接口的ireq发送数据,被测FPGA的target接口的treq接收到数据;

2. 被测FPGA的target接口的tresp发送数据,测试激励的initiator接口的iresp接收到数据;

3. 被测FPGA的initiator接口的ireq发送数据,测试激励的target接口的treq接收到数据;

4. 测试激励的target接口的tresp发送数据,被测FPGA的initiator接口的iresp接收到数据。

测试时需要根据实际功能将所有的功能进行测试,保证测试逻辑层的覆盖率。

3、实验结果

当测试激励的initiator接口的ireq以数据NWRITE_R事务发送数据0x5555AAAAEB90001F时,如图3.1所示,被测FPGA的target接口的treq端正确显示测试激励发送的数据,如图3.2所示,initiator接口的iresp接收到反馈帧。仿真波形如图3.3所示。

图3.1 IREQ端NWRITE_R波形图

图3.2 TREQ端NWRITE_R波形图

图3.3 IRESP端NWRITE_R波形图

4、结语

RapidIO 在FPGA中运用的越来越广泛,文中分析了RapidIO协议的结构,介绍了RapidIO IP核的基本框架,FPGA验证平台的搭建以及测试过的实施,为类似项目的快速理解和仿真验证提供参考。

-End-